1.4 Transistor-Logik

Achtung: Es ist nur eine Simulation für Digitaltechnik!

Die Simulation verhält sich hier nicht wie es der Elektrotechniker erwarten könnte.

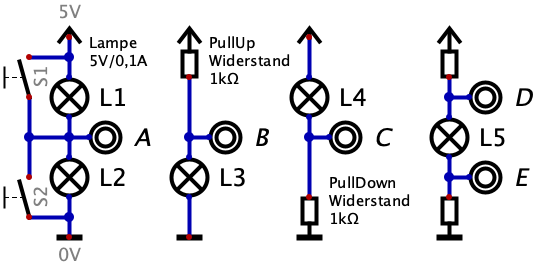

Jedes Modell hat seine Grenzen, Digital ist keine Simulation für Analoge Schaltungen und bei obigem praktischem Beispiel würde ich im Labor andere Ergebnisse erleben:

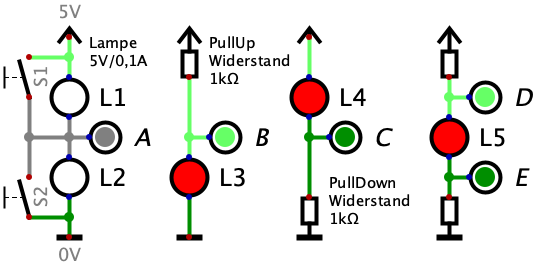

- Bei offenen Schaltern S1 und S2 würden L1 und L2 dunkel leuchten.

- L3 würde nicht leuchten und B hätte den Wert 0

- L4 würde nicht leuchten und C hätte den Wert 1

- L5 würde nicht leuchtend D und E hätten eher einen undefinierten Wert

Glühlämpchen und Relais haben keinen Innenwiderstand bei Digital?

To Do: Elektrotechnische Grundlagen, definierte und undefinierte Werte (Spannungsbereich für 0 und 1).

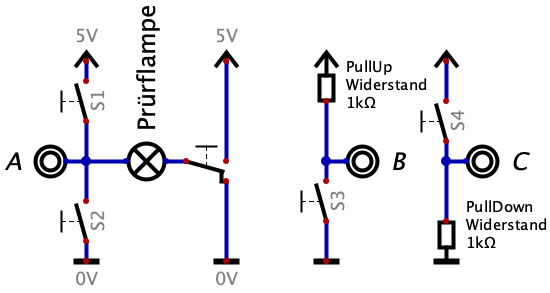

Die 3 möglichen Zustände einer Leitung in einer Digitalschaltung

Bisher gab es bei unseren Schaltungen nur die logischen Zustände 0 und 1. Bei der Testschaltung hat bei offenen Schaltern S1 und S2 A den grauen Zustand “undefiniert” bzw. “hochohmig”, weder 0 noch 1. Die Prüflampe leuchtet weder bei Referenz 0V noch 5V. Durch PullUp bzw. Pulldown Widerstand kann bei offenen Schaltern ein definierter Logikpegel erreicht werden.

Transistoren als Schalter

N-Kanal MOS Fet (NMOS) Metall-Oxid-Halbleiter-Feldeffekttransistor

ToDo: Transistoranschlüsse bezeichnen, eingängiges Bild, auch auf Unterschied Bipolartransistor eingehen.

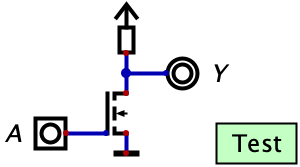

Inverter mit NMOS Transistor und PullUp Widerstand

ToDo: Wozu PullUp, Beispiel mit Flasche, Schlauch und Wasserhahn oder Klospülung?

Vorbereitung auf CMOS, dauernder Stromfluss wenn Transistor geschlossen, unterschiedliche Zeiten für 0->1 und 1->0.

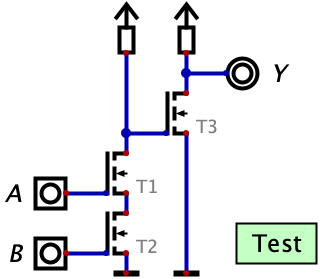

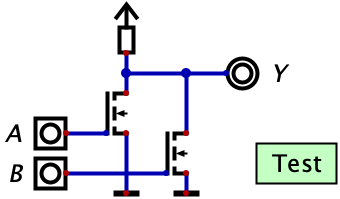

NAND und AND mit NMOS Transistoren und PullUp Widerstand

NOR und OR mit NMOS Transistoren und PullUp Widerstand

Nachteile von NMOS bzw. PMOS

- Strombedarf hoch: Wenn z.B. bei Inverter der Transistor leitet, fließt Strom durch den PullUp- bzw. PullDown-Widerstand.

- Geschwindigkeit eingeschränkt: Der PullUp- bzw. PullDown-Widerstand muss (deutlich) grösser sein als der Widerstand des durchgeschalteten Transistors. Damit ist die Umschaltzeit durch parasitäre Kapazitäten, die umgeladen werden müssen unterschiedlich bei 0->1 bzw. 1->0 Übergängen.

CMOS-Technik

Um die Nachteile der NMOS- bzw. PMOS-Technik zu eliminieren wurden die PullUp- bzw. PullDown-Widerstände durch ein komplementäres Transitornetz ersetzt.

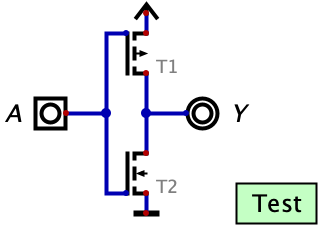

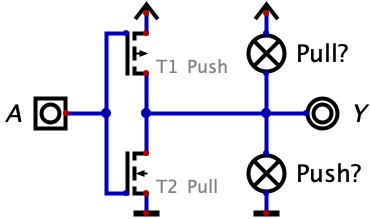

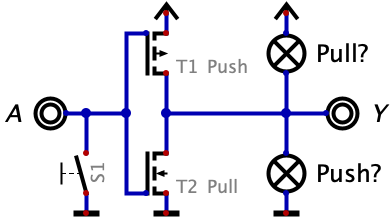

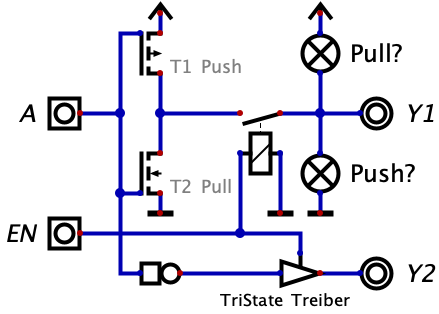

Inverter mit CMOS

Ein Transistor sollte immer durchschalten. T1 “pusht” die Versorgungspannung und damit einen möglichen Strom auf Y. T2 “pullt” Y auf GND, nimmt einen möglichen Strom auf. So einen Ausgang nennt man PushPull-Ausgang.

Beachte: A kann hier 3 Zustände annehmen: 1,0,hochohmig (grau). Wenn kein Transistor durchschaltet ist der Ausgang auch hochohmig.

ToDo: P-Kanal MOS Fet Transistor,

Beispiel mit zwei Wasserhähnen.

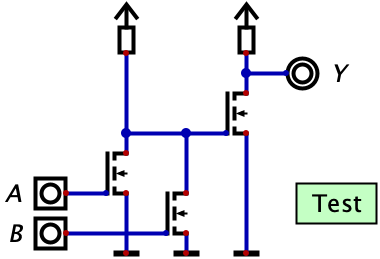

NAND und AND mit CMOS

NOR und OR mit CMOS

Vor- und Nachteile von CMOS

Entweder schalten unten (GND) die NMOS- oder oben (VCC) die PMOS-Transitoren durch. Beim Umschalten fließt kurz ein Strom (beide Transistoren leiten ein bisschen und die parasitären Kapazitäten werden umgeladen). Danach ist der Strombedarf nahe 0. Weil immer Transistoren den Strom liefern geht das schnell. Allerdings ist der Schaltungsaufwand etwas höher als bei reinen NMOS bzw. PMOS Schaltkreisen.

PushPull-Ausgang

Pull bedeutet ziehen und meint eine Leitung auf GND also 0V zu ziehen, einen Strom aufnehmen. Wenn T2 leitet wird Y auf 0V gezogen und die Pull-Lampe leuchtet. Push bedeutet schieben und meint eine Leitung auf einen Spannungspegel zu schieben, einen Strom liefern. Wenn T1 leitet wird die Y auf Versorgungsspannung geschoben und die Push-Lampe leuchtet.

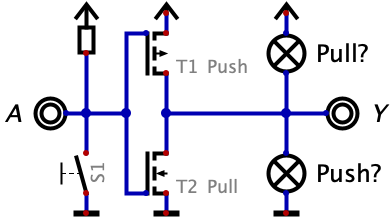

Wozu PullUp, PullDown am Eingang? Kein Floating!

Wenn S1 offen ist ist der Zustand an A und Y undefiniert (grau). Man nennt diesen Zustand auch Floating.

Floating (ohne definierten Logikpegel) Eingänge sind sehr unerwünscht, weil dabei oft beide Transistoren ein bisschen leiten und Stromverbrauch verursachen oder durch umgebende elektrische Felder zwischen 0 und 1 geschwungen wird.

Ausgänge zusammenschalten?

Warum sollte man das tun? Wenn viele Komponenten verbunden werden sollen ist es günstig sich Leitungen zu teilen: Bus-System. Dabei werden Ausgänge auf gemeinsame Leitungen aufgeschaltet. Es darf aber immer nur einer sprechen, die anderen schweigen.

CMOS-Ausgänge verbinden?

Keine gute Idee wegen Kurzschluss…

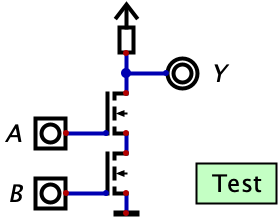

Open Drain, Open Collector Ausgang

Eine einfache Möglichkeit Ausgänge zusammen zu schalten ist sie einfach als OpenDrain bzw. OpenCollector aus zu führen. [de.wikipedia.org/wiki/Open-Collector-Ausgang] Ein PullUp-Widerstand sorgt für log. 1 wenn alle Transistoren offen sind. Diese Art Ausgang wird z.B. beim I2C-Bus verwendet.

Vorteil: Es ist einfach. Nachteil: Übergangszeit von 0->1 wird durch PullUp Widerstand bestimmt.

Erstellen Sie eine Funktionstabelle für A,B,Y.

TriState-Ausgang

Um für beide Übergänge 0->1 und 1->0 einen hohen Strom liefern zu können wäre ein PushPull-Ausgang notwendig, allerdings sollte er auch “die Klappe halten können”, hochohmig sein können, damit es zu keinen Kurzschlüssen kommt. Ein gesteuerter Schalter (Relais) könnte dies bewirken.

In Digital gibt es so ein Bauteil: TriState-Treiber

[de.wikipedia.org/wiki/Tri-State]

Es kann kräftig 0,1 liefern wenn EN=1 ist aber auch hochohmig sein wenn EN=0 ist.

In einem TriState-Treiber ist natürlich kein Relais eingebaut, das wäre zu groß und viel zu langsam. Hier ein Schaltungsbeispiel wie der Hochohmig-Zustand mit CMOS realisiert werden kann.

Fragen und Aufgaben

- Zeichnen Sie einen N-Kanal-MOS Transistor und beschreiben Sie seine Funktion. Wann leitet er?

- Zeichnen Sie einen P-Kanal-MOS Transistor und beschreiben Sie seine Funktion. Wann leitet er?

- Wozu sind PullUp-Widerstände notwendig?

- Welche Vor- und Nachteile haben CMOS- gegenüber NMOS-Schaltungen?

- Wofür sind OpenDrain- bzw. OpenCollector-Ausgänge nützlich?

- Zeichen Sie das Schaltsymbol eines TriState-Treibers und erklären Sie seine Funktion und Anwendung.

- Zeichnen Sie einen NMOS-Inverter

- Zeichnen Sie einen CMOS-Inverter

Schaltungen analysieren

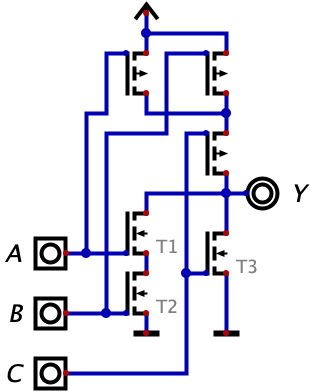

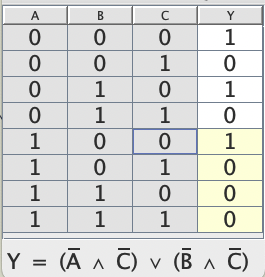

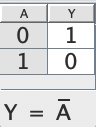

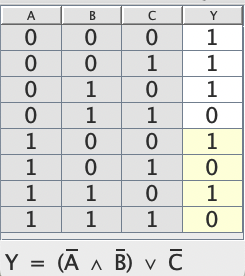

Welche Funktion hat diese Schaltung?

Erstellen Sie die Funktionstabellen und ermitteln Sie die Gleichungen in DNF.

| A | B | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | |

| 0 | 0 | 1 | |

| 0 | 1 | 0 | |

| 0 | 1 | 1 | |

| 1 | 0 | 0 | |

| 1 | 0 | 1 | |

| 1 | 1 | 0 | |

| 1 | 1 | 1 |

Lösung

Lösung

Lösung

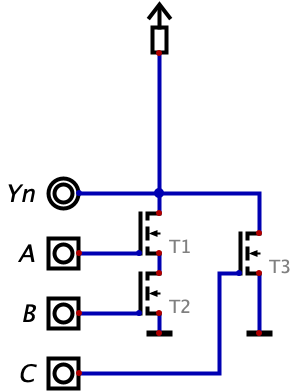

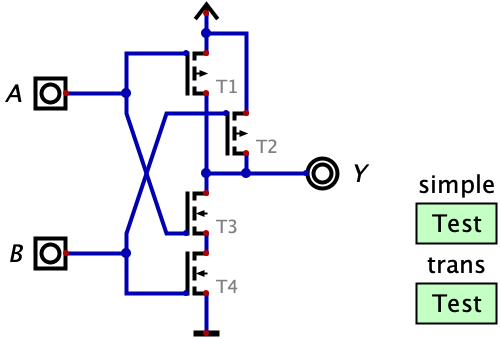

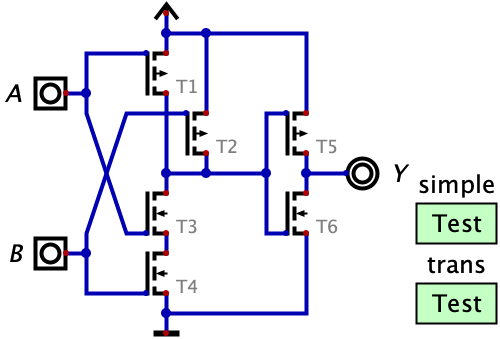

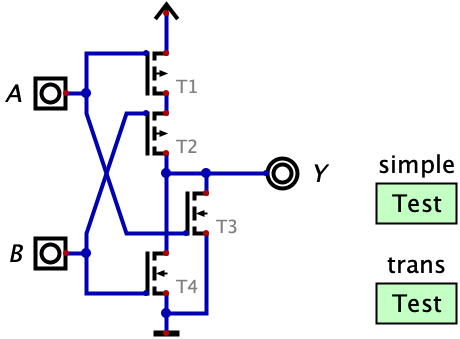

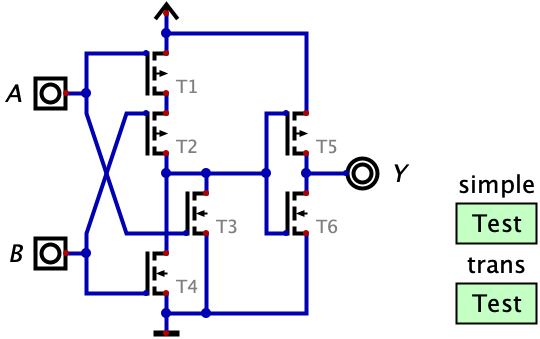

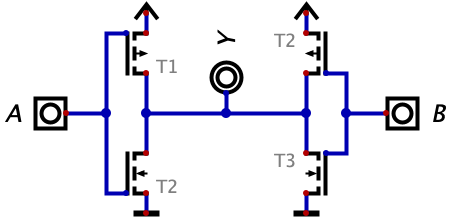

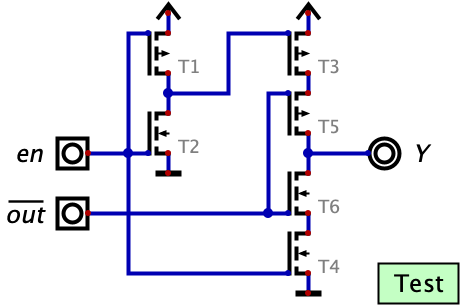

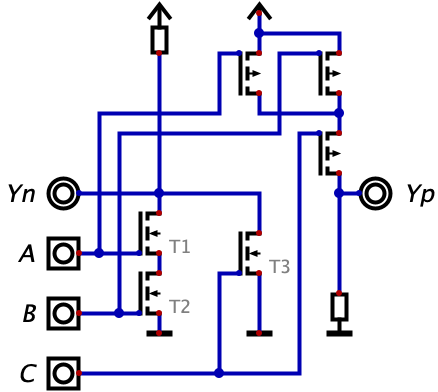

Schaltung analysieren und in CMOS erweitern

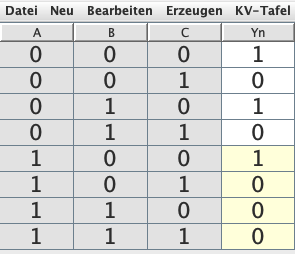

- Analysieren Sie die Schaltung und erstellen Sie eine Wertetabelle.

- Erweitern Sie die Schaltung um eine PMOS-Schaltung, die die gleiche Funktion erfüllt.

- Tipp: Reihenschaltungen in NMOS werden zu Parallelschaltungen in PMOS, Parallelschaltungen in NMOS werden zu Reihenschaltungen in PMOS.

- Vereinigen Sie beide Schaltungen zu einer CMOS-Schaltung.

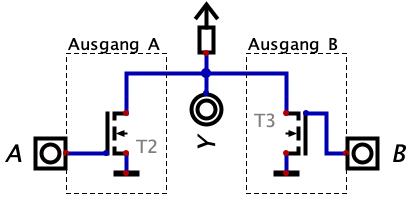

Lösung 1

Lösung 2

Lösung 3